#### **DATA SHEET**

# 128M bits DDR SDRAM

# EDD1232AAFA (4M words × 32 bits)

### **Description**

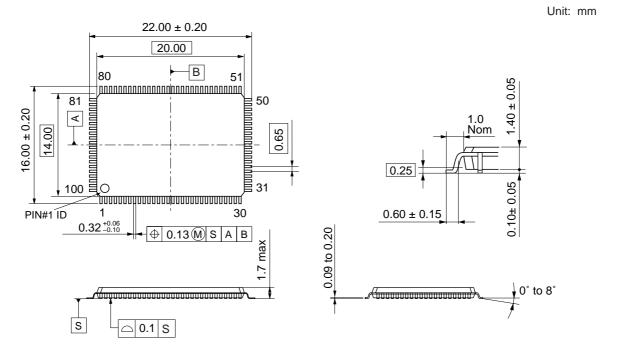

The EDD1232AAFA is a 128M bits DDR SDRAM organized as 1,048,576 words  $\times$  32 bits  $\times$  4 banks. Read and write operations are performed at the cross points of the CK and the /CK. This high-speed data transfer is realized by the 2 bits prefetch-pipelined architecture. Data strobe (DQS) both for read and write are available for high speed and reliable data bus design. By setting extended mode register, the on-chip Delay Locked Loop (DLL) can be set enable or disable. It is packaged in 100-pin plastic LQFP package.

#### **Features**

- Power supply: VDDQ =  $2.5V \pm 0.2V$ : VDD =  $2.5V \pm 0.2V$

- Data rate: 333Mbps/266Mbps (max.)

- Double Data Rate architecture; two data transfers per clock cycle

- Bi-directional, data strobe (DQS) is transmitted /received with data, to be used in capturing data at the receiver

- Data inputs, outputs, and DM are synchronized with DOS

- 4 internal banks for concurrent operation

- DQS is edge aligned with data for READs; center aligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- . Data mask (DM) for write data

- Auto precharge option for each burst access

- SSTL\_2 compatible I/O

- Programmable burst length (BL): 2, 4, 8

- Programmable /CAS latency (CL): 2, 2.5, 3

- Programmable output driver strength: half/weak

- Refresh cycles: 4096 refresh cycles/32ms

- 7.8μs maximum average periodic refresh interval

- 2 variations of refresh

- Auto refresh

- Self refresh

- LQFP package with lead free solder (Sn-Bi)

- RoHS compliant

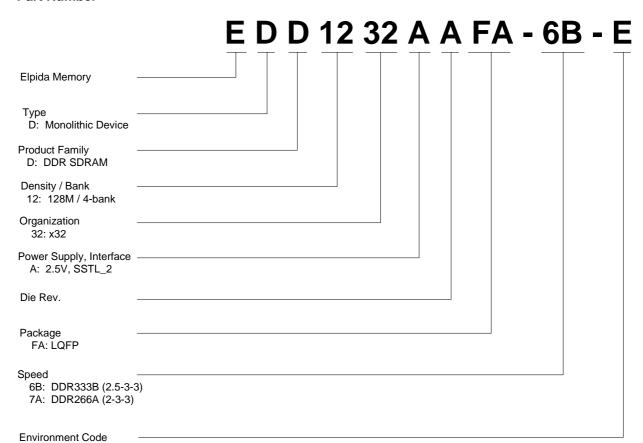

# **Ordering Information**

| Part number      | Mask<br>version | Organization (words × bits) | Internal<br>banks | Data Rate<br>Mbps (max.) | JEDEC speed bin (CL-tRCDRD-tRP) | Package         |

|------------------|-----------------|-----------------------------|-------------------|--------------------------|---------------------------------|-----------------|

| EDD1232AAFA-6B-E | Δ               | 4M × 32                     | 4                 | 333                      | DDR333B (2.5-3-3)               | 100-pin Plastic |

| EDD1232AAFA-7A-E | $\sim$          | TIVI A JZ                   | 7                 | 266                      | DDR266A (2-3-3)                 | LQFP            |

### **Part Number**

E: Lead Free

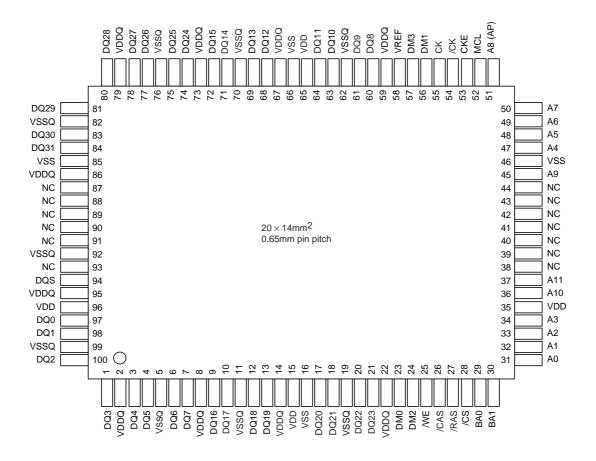

# **Pin Configurations**

/xxx indicates active low signal.

# 100-pin plastic LQFP

(Top view)

| Pin name    | Function                      | Pin name | Function                    |

|-------------|-------------------------------|----------|-----------------------------|

| A0 to A11   | Address inputs                | CK       | Clock input                 |

| BA0, BA1    | Bank select address           | /CK      | Differential Clock input    |

| DQ0 to DQ31 | Data-input/output             | CKE      | Clock enable                |

| DQS         | Input and output data strobe  | VREF     | Input reference voltage     |

| /CS         | Chip select                   | VDD      | Power for internal circuit  |

| /RAS        | Row address strobe command    | VSS      | Ground for internal circuit |

| /CAS        | Column address strobe command | VDDQ     | Power for DQ circuit        |

| /WE         | Write enable                  | VSSQ     | Ground for DQ circuit       |

| DM0 to DM3  | Input mask                    | MCL      | Must be connected with VSS  |

| NC          | No connection                 |          |                             |

# **CONTENTS**

| Description                      | 1  |

|----------------------------------|----|

| Features                         |    |

| Ordering Information             | 2  |

| Part Number                      | 2  |

| Pin Configurations               |    |

| Electrical Specifications        |    |

| Block Diagram                    | 11 |

| Pin Function                     | 12 |

| Command Operation                | 14 |

| Simplified State Diagram         | 21 |

| Operation of the DDR SDRAM       | 22 |

| Timing Waveforms                 | 41 |

| Package Drawing                  |    |

| Recommended Soldering Conditions | 48 |

#### **Electrical Specifications**

- All voltages are referenced to VSS (GND).

- After power up, wait more than 200 µs and then, execute power on sequence and CBR (Auto) refresh before proper device operation is achieved.

#### **Absolute Maximum Ratings**

| Parameter                          | Symbol | Rating       | Unit Note |

|------------------------------------|--------|--------------|-----------|

| Voltage on any pin relative to VSS | VT     | -1.0 to +3.6 | V         |

| Supply voltage relative to VSS     | VDD    | -1.0 to +3.6 | V         |

| Short circuit output current       | IOS    | 50           | mA        |

| Power dissipation                  | PD     | 1.0          | W         |

| Operating ambient temperature      | TA     | 0 to +70     | °C        |

| Storage temperature                | Tstg   | -55 to +125  | °C        |

#### Caution

Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

### Recommended DC Operating Conditions (TA = 0 to +70°C)

| Parameter                                                 | Symbol       | min.                     | typ.                      | max.               | Unit | Notes |

|-----------------------------------------------------------|--------------|--------------------------|---------------------------|--------------------|------|-------|

| Supply voltage                                            | VDD,<br>VDDQ | 2.3                      | 2.5                       | 2.7                | ٧    | 1     |

|                                                           | VSS,<br>VSSQ | 0                        | 0                         | 0                  | V    |       |

| Input reference voltage                                   | VREF         | $0.49 \times VDDQ$       | $0.50 \times \text{VDDQ}$ | $0.51 \times VDDQ$ | V    | _     |

| Termination voltage                                       | VTT          | VREF - 0.04              | VREF                      | VREF + 0.04        | V    |       |

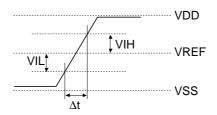

| Input high voltage                                        | VIH (DC)     | VREF + 0.15              | _                         | VDDQ + 0.3         | V    | 2     |

| Input low voltage                                         | VIL (DC)     | -0.3                     | _                         | VREF - 0.15        | V    | 3     |

| Input voltage level,<br>CK and /CK inputs                 | VIN (DC)     | -0.3                     | _                         | VDDQ + 0.3         | V    | 4     |

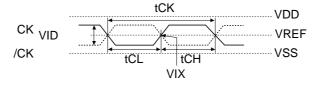

| Input differential cross point voltage, CK and /CK inputs | VIX (DC)     | $0.5 \times VDDQ - 0.2V$ | $0.5 \times VDDQ$         | 0.5 × VDDQ + 0.2V  | V    |       |

| Input differential voltage,<br>CK and /CK inputs          | VID (DC)     | 0.36                     | _                         | VDDQ + 0.6         | V    | 5, 6  |

Notes: 1. VDDQ must be lower than or equal to VDD.

- 2. VIH is allowed to exceed VDD up to 3.6V for the period shorter than or equal to 5ns.

- 3. VIL is allowed to outreach below VSS down to -1.0V for the period shorter than or equal to 5ns.

- 4. VIN (DC) specifies the allowable DC execution of each differential input.

- 5. VID (DC) specifies the input differential voltage required for switching.

- 6. VIH (CK) min assumed over VREF + 0.18V, VIL (CK) max assumed under VREF 0.18V if measurement.

### DC Characteristics 1 (TA = 0 to $\pm$ 70°C, VDD, VDDQ = 2.5V $\pm$ 0.2V, VSS, VSSQ = 0V)

| Parameter                                 | Symbol | Grade      | max.       | Unit | Test condition                                  | Notes      |

|-------------------------------------------|--------|------------|------------|------|-------------------------------------------------|------------|

| Operating current (ACT-PRE                | ) IDD0 |            | 120        | mA   | CKE ≥ VIH,<br>tRC = tRC (min.)                  | 1, 2, 9    |

| Operating current (ACT-READ-PRE)          | IDD1   |            | 160        | mA   | CKE ≥ VIH, BL = 4,CL = 2.5,<br>tRC = tRC (min.) | 1, 2, 5    |

| Idle power down standby current           | IDD2P  |            | 20         | mA   | CKE ≤ VIL                                       | 4          |

| Floating idle standby current             | IDD2F  |            | 40         | mA   | CKE ≥ VIH, /CS ≥ VIH<br>DQ, DQS, DM = VREF      | 4, 5       |

| Quiet idle standby current                | IDD2Q  |            | 35         | mA   | CKE ≥ VIH, /CS ≥ VIH<br>DQ, DQS, DM = VREF      | 4, 10      |

| Active power down standby current         | IDD3P  |            | 30         | mA   | CKE ≤ VIL                                       | 3          |

| Active standby current                    | IDD3N  |            | 100        | mA   | CKE ≥ VIH, /CS ≥ VIH<br>tRAS = tRAS (max.)      | 3, 5, 6    |

| Operating current (Burst read operation)  | IDD4R  | -6B<br>-7A | 330<br>260 | mA   | CKE ≥ VIH, BL = 2, CL = 2.5                     | 1, 2, 5, 6 |

| Operating current (Burst write operation) | IDD4W  | -6B<br>-7A | 330<br>260 | mA   | CKE ≥ VIH, BL = 2,CL = 2.5                      | 1, 2, 5, 6 |

| Auto Refresh current                      | IDD5   |            | 200        | mA   | tRFC = tRFC (min.),<br>Input ≤ VIL or ≥ VIH     |            |

| Self refresh current                      | IDD6   |            | 3          | mA   | Input ≥ VDD – 0.2 V<br>Input ≤ 0.2 V            |            |

| Operating current (4 banks interleaving)  | IDD7A  | -6B<br>-7A | 380<br>375 | mA   | BL = 4                                          | 1, 5, 6, 7 |

Notes: 1. These IDD data are measured under condition that DQ pins are not connected.

- 2. One bank operation.

- 3. One bank active.

- 4. All banks idle.

- 5. Command/Address transition once per one clock cycle.

- 6. DQ, DM and DQS transition twice per one clock cycle.

- 7. 4 banks active. Only one bank is running at tRC = tRC (min.)

- 8. The IDD data on this table are measured with regard to tCK = tCK (min.) in general.

- 9. Command/Address transition once every two clock cycle.

- 10. Command/Address stable at ≥ VIH or ≤ VIL.

### DC Characteristics 2 (TA = 0 to $+70^{\circ}$ C, VDD, VDDQ = 2.5V $\pm$ 0.2V, VSS, VSSQ = 0V)

| Parameter              | Symbol | min.       | max. | Unit | Test condition    | Notes |

|------------------------|--------|------------|------|------|-------------------|-------|

| Input leakage current  | ILI    | -2         | 2    | μΑ   | VDD ≥ VIN ≥ VSS   |       |

| Output leakage current | ILO    | <b>-</b> 5 | 5    | μΑ   | VDDQ ≥ VOUT ≥ VSS |       |

| Output high current    | IOH    | -15.2      | _    | mA   | VOUT = 1.95V      |       |

| Output low current     | IOL    | 15.2       | _    | mA   | VOUT = 0.35V      |       |

# Pin Capacitance (TA = +25°C, VDD, VDDQ = $2.5V \pm 0.2V$ )

| Parameter                      | Symbol | Pins                 | min. | typ. | max. | Unit | Notes |

|--------------------------------|--------|----------------------|------|------|------|------|-------|

| Input capacitance              | CI1    | CK, /CK              | 1.0  | _    | 5.0  | pF   | 1     |

|                                | CI2    | All other input pins | 1.0  | _    | 4.0  | pF   | 1     |

| Data input/output capacitance  | CI/O   | DQ, DM, DQS          | 4.0  | _    | 5.0  | pF   | 1, 2  |

| Delta input/output capacitance | Cdio   | DQ, DM, DQS          | _    | _    | 0.5  | pF   | 1     |

Notes: 1. These parameters are measured on conditions: f = 100MHz, VOUT = VDDQ/2,  $\Delta$ VOUT = 0.2V,  $TA = +25^{\circ}C$ .

2. DOUT circuits are disabled.

# AC Characteristics (TA = 0 to +70°C, VDD, VDDQ = $2.5V \pm 0.2V$ , VSS, VSSQ = 0V)

|                                                |        | -6B               |        | -7A               |        |      |       |

|------------------------------------------------|--------|-------------------|--------|-------------------|--------|------|-------|

| Parameter                                      | Symbol | min.              | max.   | min.              | max.   | Unit | Notes |

| Clock cycle time<br>(CL = 2)                   | tCK    | 7.5               | 12     | 7.5               | 12     | ns   | 10    |

| (CL = 2.5)                                     | tCK    | 6                 | 12     | 7.5               | 12     | ns   |       |

| (CL = 3)                                       | tCK    | 6                 | 12     | 7.5               | 12     | ns   |       |

| CK high-level width                            | tCH    | 0.45              | 0.55   | 0.45              | 0.55   | tCK  |       |

| CK low-level width                             | tCL    | 0.45              | 0.55   | 0.45              | 0.55   | tCK  |       |

| CK half period                                 | tHP    | min<br>(tCH, tCL) | _      | min<br>(tCH, tCL) | _      | tCK  |       |

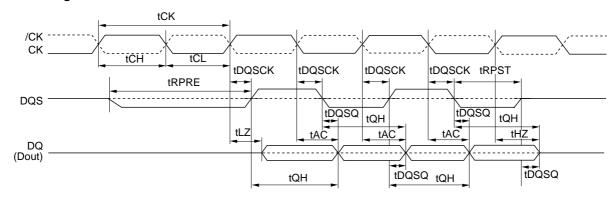

| DQ output access time from CK, /CK             | tAC    | -0.7              | 0.7    | -0.75             | 0.75   | ns   | 2, 11 |

| DQS output access time from CK, /CK            | tDQSCK | -0.7              | 0.7    | -0.75             | 0.75   | ns   | 2, 11 |

| DQS to DQ skew                                 | tDQSQ  | _                 | 0.45   | _                 | 0.5    | ns   | 3     |

| DQ/DQS output hold time from DQS               | tQH    | tHP - 0.55        | _      | tHP - 0.75        | _      | ns   |       |

| Data-out high-impedance time from CK, /CK      | tHZ    | _                 | 0.7    | _                 | 0.75   | ns   | 5, 11 |

| Data-out low-impedance time from CK, /CK       | tLZ    | -0.7              | 0.7    | -0.75             | 0.75   | ns   | 6, 11 |

| Read preamble                                  | tRPRE  | 0.9               | 1.1    | 0.9               | 1.1    | tCK  |       |

| Read postamble                                 | tRPST  | 0.4               | 0.6    | 0.4               | 0.6    | tCK  |       |

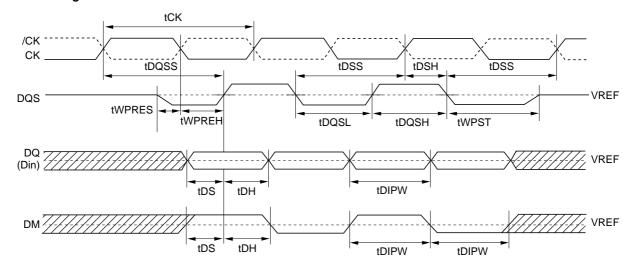

| DQ and DM input setup time                     | tDS    | 0.45              | _      | 0.5               | _      | ns   | 8     |

| DQ and DM input hold time                      | tDH    | 0.45              | _      | 0.5               | _      | ns   | 8     |

| DQ and DM input pulse width                    | tDIPW  | 1.75              | _      | 1.75              | _      | ns   | 7     |

| Write preamble setup time                      | tWPRES | 0                 | _      | 0                 | _      | ns   |       |

| Write preamble hold time                       | tWPREH | 0.25              | _      | 0.25              | _      | tCK  |       |

| Write postamble                                | tWPST  | 0.4               | 0.6    | 0.4               | 0.6    | tCK  | 9     |

| Write command to first DQS latching transition | tDQSS  | 0.75              | 1.25   | 0.75              | 1.25   | tCK  |       |

| DQS falling edge to CK setup time              | tDSS   | 0.2               | _      | 0.2               | _      | tCK  |       |

| DQS falling edge hold time from CK             | tDSH   | 0.2               | _      | 0.2               | _      | tCK  |       |

| DQS input high pulse width                     | tDQSH  | 0.35              | _      | 0.35              | _      | tCK  |       |

| DQS input low pulse width                      | tDQSL  | 0.35              |        | 0.35              | _      | tCK  |       |

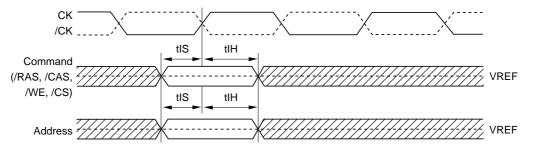

| Address and control input setup time           | tIS    | 1.0               | _      | 1.0               | _      | ns   | 8     |

| Address and control input hold time            | tIH    | 1.0               | _      | 1.0               |        | ns   | 8     |

| Address and control input pulse width          | tIPW   | 2.2               | _      | 2.2               |        | ns   | 7     |

| Mode register set command cycle time           | tMRD   | 2                 | _      | 2                 |        | tCK  |       |

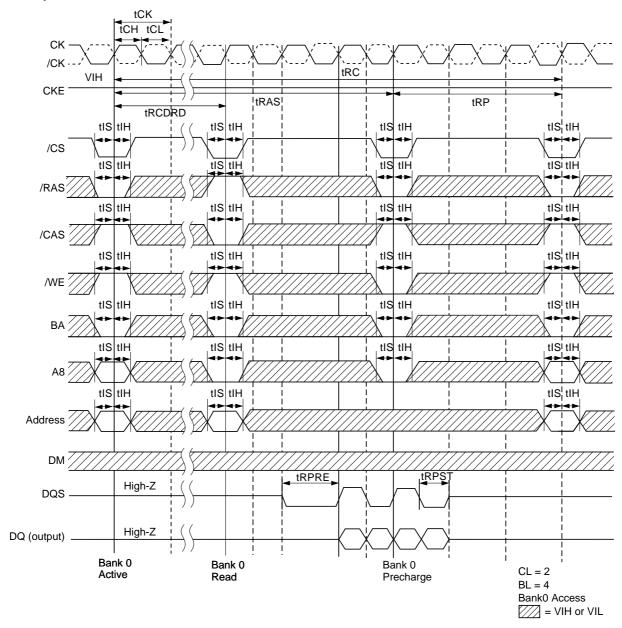

| Active to Precharge command period             | tRAS   | 42                | 120000 | 45                | 120000 | ns   |       |

|                                                    |        | -6B         |      | -7A         |      | _    |       |

|----------------------------------------------------|--------|-------------|------|-------------|------|------|-------|

| Parameter                                          | Symbol | min.        | max. | min.        | max. | Unit | Notes |

| Active to Active/Auto refresh command period       | tRC    | 60          | _    | 67.5        | _    | ns   |       |

| Auto refresh to Active/Auto refresh command period | tRFC   | 72          | _    | 75          | _    | ns   |       |

| Active to Read delay                               | tRCDRD | 18          | _    | 20          | _    | ns   |       |

| Active to Write delay                              | tRCDWR | 12          | _    | 15          | _    | ns   |       |

| Precharge to active command period                 | tRP    | 18          | _    | 20          | _    | ns   |       |

| Active to Autoprecharge delay                      | tRAP   | tRCDRD min. | _    | tRCDRD min. | _    | ns   |       |

| Active to active command period                    | tRRD   | 12          | _    | 15          | _    | ns   |       |

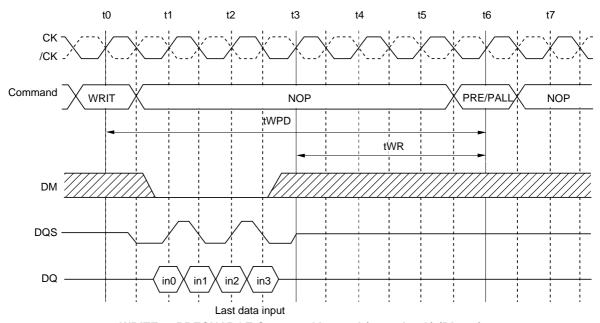

| Write recovery time                                | tWR    | 18          | _    | 20          | _    | ns   |       |

| Auto precharge write recovery and precharge time   | tDAL   | 6           | _    | 6           | _    | tCK  |       |

| Internal write to Read command delay               | tWTR   | 2           | _    | 2           | _    | tCK  |       |

| Average periodic refresh interval                  | tREF   | _           | 7.8  | _           | 7.8  | μs   |       |

- Notes: 1. On all AC measurements, we assume the test conditions shown in the next page. For timing parameter definitions, see 'Timing Waveforms' section.

- 2. This parameter defines the signal transition delay from the cross point of CK and /CK. The signal transition is defined to occur when the signal level crossing VTT.

- 3. The timing reference level is VTT.

- 4. Output valid window is defined to be the period between two successive transition of data out or DQS (read) signals. The signal transition is defined to occur when the signal level crossing VTT.

- 5. tHZ is defined as DOUT transition delay from Low-Z to High-Z at the end of read burst operation. The timing reference is cross point of CK and /CK. This parameter is not referred to a specific DOUT voltage level, but specify when the device output stops driving.

- tLZ is defined as DOUT transition delay from High-Z to Low-Z at the beginning of read operation. This parameter is not referred to a specific DOUT voltage level, but specify when the device output begins driving.

- 7. Input valid windows is defined to be the period between two successive transition of data input or DQS (write) signals. The signal transition is defined to occur when the signal level crossing VREF.

- 8. The timing reference level is VREF.

- 9. The transition from Low-Z to High-Z is defined to occur when the device output stops driving. A specific reference voltage to judge this transition is not given.

- 10. tCK (max.) is determined by the lock range of the DLL. Beyond this lock range, the DLL operation is not assured.

- 11. tCK = tCK (min) when these parameters are measured. Otherwise, absolute minimum values of these values are 10% of tCK.

- 12. VDD is assumed to be 2.5V  $\pm$  0.2V. VDD power supply variation per cycle expected to be less than 0.4V/400 cycle.

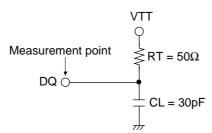

### **Test Conditions**

| Parameter                                                 | Symbol   | Value       | Unit |

|-----------------------------------------------------------|----------|-------------|------|

| Input reference voltage                                   | VREF     | VDDQ/2      | V    |

| Termination voltage                                       | VTT      | VREF        | V    |

| Input high voltage                                        | VIH (AC) | VREF + 0.31 | V    |

| Input low voltage                                         | VIL (AC) | VREF - 0.31 | V    |

| Input differential voltage, CK and /CK inputs             | VID (AC) | 0.62        | V    |

| Input differential cross point voltage, CK and /CK inputs | VIX (AC) | VREF        | V    |

| Input signal slew rate                                    | SLEW     | 1           | V/ns |

$SLEW = (VIH (AC) - VIL (AC))/\Delta t$

**Input Waveforms and Output Load**

# **Timing Parameter Measured in Clock Cycle**

# Number of clock cycle

| tCK                                                                     |        | 6ns      |      | 7.5ns    |      |      |

|-------------------------------------------------------------------------|--------|----------|------|----------|------|------|

| Parameter                                                               | Symbol | min.     | max. | min.     | max. | Unit |

| Write to pre-charge command delay (same bank)                           | tWPD   | 4 + BL/2 | _    | 3 + BL/2 | _    | tCK  |

| Read to pre-charge command delay (same bank)                            | tRPD   | BL/2     | _    | BL/2     | _    | tCK  |

| Write to read command delay (to input all data)                         | tWRD   | 3 + BL/2 | _    | 3 + BL/2 | _    | tCK  |

| Burst stop command to write command delay (CL = 2)                      | tBSTW  | _        | _    | 2        | _    | tCK  |

| (CL = 2.5)                                                              | tBSTW  | 3        | _    | 3        | _    | tCK  |

| (CL = 3)                                                                | tBSTW  | 3        | _    | 3        | _    | tCK  |

| Burst stop command to DQ High-Z (CL = 2)                                | tBSTZ  | _        | _    | 2        | 2    | tCK  |

| (CL = 2.5)                                                              | tBSTZ  | 2.5      | 2.5  | 2.5      | 2.5  | tCK  |

| (CL = 3)                                                                | tBSTZ  | 3        | 3    | 3        | 3    | tCK  |

| Read command to write command delay<br>(to output all data)<br>(CL = 2) | tRWD   | _        | _    | 2 + BL/2 | _    | tCK  |

| (CL = 2.5)                                                              | tRWD   | 3 + BL/2 | _    | 3 + BL/2 | _    | tCK  |

| (CL = 3)                                                                | tRWD   | 3 + BL/2 | _    | 3 + BL/2 | _    | tCK  |

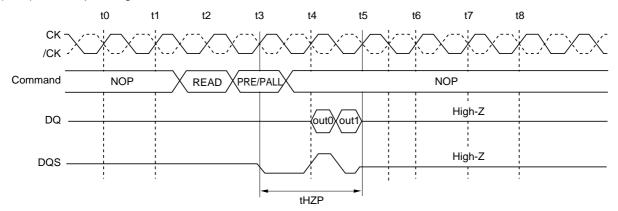

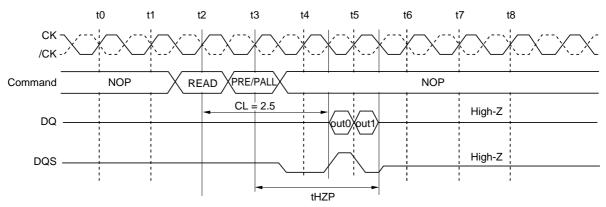

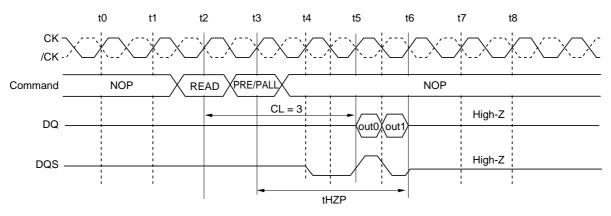

| Pre-charge command to High-Z (CL = 2)                                   | tHZP   | _        | _    | 2        | 2    | tCK  |

| (CL = 2.5)                                                              | tHZP   | 2.5      | 2.5  | 2.5      | 2.5  | tCK  |

| (CL = 3)                                                                | tHZP   | 3        | 3    | 3        | 3    | tCK  |

| Write command to data in latency                                        | tWCD   | 1        | 1    | 1        | 1    | tCK  |

| Write recovery time                                                     | tWR    | 3        | _    | 3        | _    | tCK  |

| DM to data in latency                                                   | tDMD   | 0        | 0    | 0        | 0    | tCK  |

| Mode register set command cycle time                                    | tMRD   | 2        | _    | 2        | _    | tCK  |

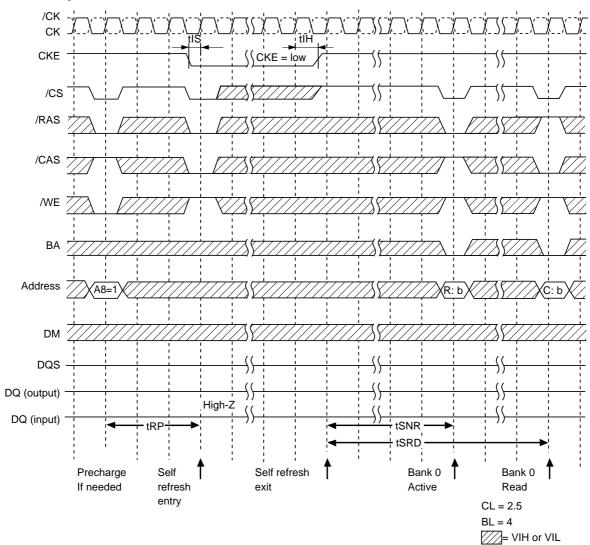

| Self refresh exit to non-read command                                   | tSNR   | 12       | _    | 10       | _    | tCK  |

| Self refresh exit to read command                                       | tSRD   | 200      | _    | 200      | _    | tCK  |

| Power down entry                                                        | tPDEN  | 1        | 1    | 1        | 1    | tCK  |

| Power down exit to command input                                        | tPDEX  | 1        | _    | 1        | _    | tCK  |

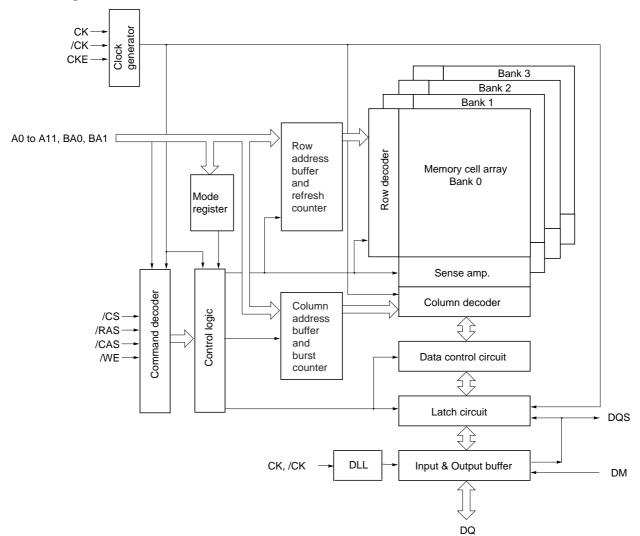

# **Block Diagram**

#### Pin Function

#### CK, /CK (input pins)

The CK and the /CK are the master clock inputs. All inputs except DM, DQS and DQs are referred to the cross point of the CK rising edge and the /CK falling edge. When a read operation, DQS and DQs are referred to the cross point of the CK and the /CK. When a write operation, DQS and DQs are referred to the cross point of the DQS and the VREF level. DQS for write operation is referred to the cross point of the CK and the /CK. CK is the master clock input to this pin. The other input signals are referred at CK rising edge.

#### /CS (input pin)

When /CS is Low, commands and data can be input. When /CS is High, all inputs are ignored. However, internal operations (bank active, burst operations, etc.) are held.

#### /RAS, /CAS, and /WE (input pins)

These pins define operating commands (read, write, etc.) depending on the combinations of their voltage levels. See "Command operation".

### A0 to A11 (input pins)

Row address (AX0 to AX11) is determined by the A0 to the A11 level at the cross point of the CK rising edge and the /CK falling edge in a bank active command cycle. Column address (See "Address Pins Table") is loaded via the A0 to the A7 at the cross point of the CK rising edge and the /CK falling edge in a read or a write command cycle. This column address becomes the starting address of a burst operation.

#### [Address Pins Table]

#### Address (A0 to A11)

| Part number | Row address | Column address |

|-------------|-------------|----------------|

| EDD1232AAFA | AX0 to AX11 | AY0 to AY7     |

#### A8 (AP) (input pin)

A8 defines the precharge mode when a precharge command, a read command or a write command is issued. If A8 = High when a precharge command is issued, all banks are precharged. If A8 = Low when a precharge command is issued, only the bank that is selected by BA1/BA0 is precharged. If A8 = High when read or write command, autoprecharge function is enabled. While A8 = Low, auto-precharge function is disabled.

#### BA0 and BA1 (input pins)

BA0, BA1 are bank select signals (BA). The memory array is divided into bank 0, bank 1, bank 2 and bank 3. (See Bank Select Signal Table)

#### [Bank Select Signal Table]

|        | BA0 | BA1 |

|--------|-----|-----|

| Bank 0 | L   | L   |

| Bank 1 | Н   | L   |

| Bank 2 | L   | Н   |

| Bank 3 | Н   | Н   |

Remark: H: VIH. L: VIL.

#### CKE (input pin)

This pin determines whether or not the next CK is valid. If CKE is High, the next CK rising edge is valid. If CKE is Low. CKE controls power down and self-refresh. The power down and the self-refresh commands are entered when the CKE is driven Low and exited when it resumes to High. CKE must be maintained high throughout read or write access.

The CKE level must be kept for 1 CK cycle at least, that is, if CKE changes at the cross point of the CK rising edge and the /CK falling edge with proper setup time tIS, by the next CK rising edge CKE level must be kept with proper hold time tIH.

### DM (input pin)

DM is the reference signal of the data input mask function. DM is sampled at the cross point of DQS and VREF.

#### DQ0 to DQ31 (input/output pins)

Data is input to and output from these pins.

### DQS (input and output pin)

DQS provides the read data strobe (as output) and the write data strobe (as input).

#### VDD, VSS, VDDQ, VSSQ (Power supply)

VDD and VSS are power supply pins for internal circuits. VDDQ and VSSQ are power supply pins for the output buffers.

#### MCL (input pins)

This pin must be connected with VSS. A connection with any level other than VSS may result in undefined operation.

#### **Command Operation**

#### **Command Truth Table**

DDR SDRAM recognize the following commands specified by the /CS, /RAS, /CAS, /WE and address pins. All other combinations than those in the table below are illegal.

|                                    |        | CKE   |       | _ |      |      |     |     |     |    |         |

|------------------------------------|--------|-------|-------|---|------|------|-----|-----|-----|----|---------|

| Command                            | Symbol | n – 1 | – 1 n |   | /RAS | /CAS | /WE | BA1 | BA0 | AP | Address |

| Ignore command                     | DESL   | Н     | Н     | Н | ×    | ×    | ×   | ×   | ×   | ×  | ×       |

| No operation                       | NOP    | Н     | Н     | L | Н    | Н    | Н   | ×   | ×   | ×  | ×       |

| Burst stop in read command         | BST    | Н     | Н     | L | Н    | Н    | L   | ×   | ×   | ×  | ×       |

| Column address and read command    | READ   | Н     | Н     | L | Н    | L    | Н   | V   | V   | L  | V       |

| Read with auto-precharge           | READA  | Н     | Н     | L | Н    | L    | Н   | V   | V   | Н  | V       |

| Column address and write command   | WRIT   | Н     | Н     | L | Н    | L    | L   | V   | V   | L  | V       |

| Write with auto-precharge          | WRITA  | Н     | Н     | L | Н    | L    | L   | V   | V   | Н  | V       |

| Row address strobe and bank active | ACT    | Н     | Н     | L | L    | Н    | Н   | V   | V   | V  | V       |

| Precharge select bank              | PRE    | Н     | Н     | L | L    | Н    | L   | V   | V   | L  | ×       |

| Precharge all bank                 | PALL   | Н     | Н     | L | L    | Н    | L   | ×   | ×   | Н  | ×       |

| Refresh                            | REF    | Н     | Н     | L | L    | L    | Н   | ×   | ×   | ×  | ×       |

|                                    | SELF   | Н     | L     | L | L    | L    | Н   | ×   | ×   | ×  | ×       |

| Mode register set                  | MRS    | Н     | Н     | L | L    | L    | L   | L   | L   | L  | V       |

|                                    | EMRS   | Н     | Н     | L | L    | L    | L   | L   | Н   | L  | V       |

Remark: H: VIH. L: VIL. x: VIH or VIL V: Valid address input Note: The CKE level must be kept for 1 CK cycle at least.

#### Ignore command [DESL]

When /CS is High at the cross point of the CK rising edge and the VREF level, every input are neglected and internal status is held.

#### No operation [NOP]

As long as this command is input at the cross point of the CK rising edge and the VREF level, address and data input are neglected and internal status is held.

#### Burst stop in read operation [BST]

This command stops a burst read operation, which is not applicable for a burst write operation.

#### Column address strobe and read command [READ]

This command starts a read operation. The start address of the burst read is determined by the column address (See "Address Pins Table" in Pin Function) and the bank select address. After the completion of the read operation, the output buffer becomes High-Z.

# Read with auto-precharge [READA]

This command starts a read operation. After completion of the read operation, precharge is automatically executed.

# Column address strobe and write command [WRIT]

This command starts a write operation. The start address of the burst write is determined by the column address (See "Address Pins Table" in Pin Function) and the bank select address.

# Write with auto-precharge [WRITA]

This command starts a write operation. After completion of the write operation, precharge is automatically executed.

**ELPIDA**

#### Row address strobe and bank activate [ACT]

This command activates the bank that is selected by BA0, BA1 and determines the row address (AX0 to AX11). (See Bank Select Signal Table)

#### Precharge selected bank [PRE]

This command starts precharge operation for the bank selected by BA0, BA1. (See Bank Select Signal Table)

#### [Bank Select Signal Table]

|        | BA0 | BA1 |

|--------|-----|-----|

| Bank 0 | L   | L   |

| Bank 1 | Н   | L   |

| Bank 2 | L   | Н   |

| Bank 3 | Н   | Н   |

Remark: H: VIH. L: VIL.

#### Precharge all banks [PALL]

This command starts a precharge operation for all banks.

### Refresh [REF/SELF]

This command starts a refresh operation. There are two types of refresh operation, one is auto-refresh, and another is self-refresh. For details, refer to the CKE truth table section.

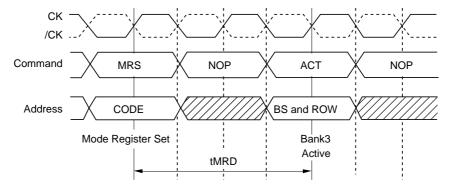

#### Mode register set/Extended mode register set [MRS/EMRS]

The DDR SDRAM has the two mode registers, the mode register and the extended mode register, to defines how it works. The both mode registers are set through the address pins (the A0 to the A11, BA0 to BA1) in the mode register set cycle. For details, refer to "Mode register and extended mode register set".

#### **CKE Truth Table**

|               |                            | CKE   |   |     |      |      |     |         |       |

|---------------|----------------------------|-------|---|-----|------|------|-----|---------|-------|

| Current state | Command                    | n – 1 | n | /CS | /RAS | /CAS | /WE | Address | Notes |

| Idle          | Auto-refresh command (REF) | Н     | Н | L   | L    | L    | Н   | ×       | 2     |

| Idle          | Self-refresh entry (SELF)  | Н     | L | L   | L    | L    | Н   | ×       | 2     |

| Idle          | Power down entry (PDEN)    | Н     | L | L   | Н    | Н    | Н   | ×       |       |

|               |                            | Н     | L | Н   | ×    | ×    | ×   | ×       |       |

| Self refresh  | Self refresh exit (SELFX)  | L     | Н | L   | Н    | Н    | Н   | ×       |       |

|               |                            | L     | Н | Н   | ×    | ×    | ×   | ×       |       |

| Power down    | Power down exit (PDEX)     | L     | Н | L   | Н    | Н    | Н   | ×       |       |

|               |                            | L     | Н | Н   | ×    | X    | ×   | ×       |       |

Remark: H: VIH. L: VIL. x: VIH or VIL.

Notes: 1. All the banks must be in IDLE before executing this command.

2. The CKE level must be kept for 1 CK cycle at least.

### **Function Truth Table**

The following tables show the operations that are performed when each command is issued in each state of the DDR SDRAM.

| Current state                           | /CS | /RAS | /CAS | /WE | Address    | Command    | Operation                   | Next state                    |

|-----------------------------------------|-----|------|------|-----|------------|------------|-----------------------------|-------------------------------|

| Precharging* <sup>1</sup>               | Н   | ×    | ×    | ×   | ×          | DESL       | NOP                         | ldle                          |

|                                         | L   | Н    | Н    | Н   | ×          | NOP        | NOP                         | ldle                          |

|                                         | L   | Н    | Н    | L   | ×          | BST        | ILLEGAL*11                  | _                             |

|                                         | L   | Н    | L    | Н   | BA, CA, A8 | READ/READA | ILLEGAL*11                  | _                             |

|                                         | L   | Н    | L    | L   | BA, CA, A8 | WRIT/WRITA | ILLEGAL*11                  | _                             |

|                                         | L   | L    | Н    | Н   | BA, RA     | ACT        | ILLEGAL*11                  | _                             |

|                                         | L   | L    | Н    | L   | BA, A8     | PRE, PALL  | NOP                         | ldle                          |

|                                         | L   | L    | L    | ×   | ×          |            | ILLEGAL                     | _                             |

| Idle*2                                  | Н   | ×    | ×    | ×   | ×          | DESL       | NOP                         | ldle                          |

|                                         | L   | Н    | Н    | Н   | ×          | NOP        | NOP                         | ldle                          |

|                                         | L   | Н    | Н    | L   | ×          | BST        | ILLEGAL*11                  | _                             |

|                                         | L   | Н    | L    | Н   | BA, CA, A8 | READ/READA | ILLEGAL*11                  | _                             |

|                                         | L   | Н    | L    | L   | BA, CA, A8 | WRIT/WRITA | ILLEGAL*11                  | _                             |

|                                         | L   | L    | Н    | Н   | BA, RA     | ACT        | Activating                  | Active                        |

|                                         | L   | L    | Н    | L   | BA, A8     | PRE, PALL  | NOP                         | ldle                          |

|                                         | L   | L    | L    | Н   | ×          | REF, SELF  | Refresh/<br>Self refresh*12 | Idle/<br>Self refresh         |

|                                         | L   | L    | L    | L   | MODE       | MRS        | Mode register set*12        | ldle                          |

| Refresh<br>(auto-refresh)* <sup>3</sup> | Н   | ×    | ×    | ×   | ×          | DESL       | NOP                         | Idle                          |

|                                         | L   | Н    | Н    | Н   | ×          | NOP        | NOP                         | ldle                          |

|                                         | L   | Н    | Н    | L   | ×          | BST        | ILLEGAL                     | _                             |

|                                         | L   | Н    | L    | ×   | ×          |            | ILLEGAL                     | _                             |

|                                         | L   | L    | ×    | ×   | ×          |            | ILLEGAL                     | _                             |

| Activating* <sup>4</sup>                | Н   | ×    | ×    | ×   | ×          | DESL       | NOP                         | Active                        |

|                                         | L   | Н    | Н    | Н   | ×          | NOP        | NOP                         | Active                        |

|                                         | L   | Н    | Н    | L   | ×          | BST        | ILLEGAL*11                  | _                             |

|                                         | L   | Н    | L    | Н   | BA, CA, A8 | READ/READA | ILLEGAL*11                  | _                             |

|                                         | L   | Н    | L    | L   | BA, CA, A8 | WRIT/WRITA | ILLEGAL*11                  | _                             |

|                                         | L   | L    | Н    | Н   | BA, RA     | ACT        | ILLEGAL*11                  | _                             |

|                                         | L   | L    | Н    | L   | BA, A8     | PRE, PALL  | ILLEGAL*11                  | _                             |

|                                         | L   | L    | L    | ×   | ×          |            | ILLEGAL                     | _                             |

| Active*5                                | Н   | ×    | ×    | ×   | ×          | DESL       | NOP                         | Active                        |

|                                         | L   | Н    | Н    | Н   | ×          | NOP        | NOP                         | Active                        |

|                                         | L   | Н    | Н    | L   | ×          | BST        | ILLEGAL                     | Active                        |

|                                         | L   | Н    | L    | Н   | BA, CA, A8 | READ/READA | Starting read operation     | Read/READA                    |

|                                         | L   | Н    | L    | L   | BA, CA, A8 | WRIT/WRITA | Starting write operation    | Write recovering/ precharging |

|                                         | L   | L    | Н    | Н   | BA, RA     | ACT        | ILLEGAL*11                  | _                             |

|                                         | L   | L    | Н    | L   | BA, A8     | PRE, PALL  | Pre-charge                  | Idle                          |

|                                         | L   | L    | L    | ×   | ×          |            | ILLEGAL                     | _                             |

# EDD1232AAFA

| Current state                               | /CS | /RAS | /CAS | /WE | Address    | Command    | Operation                                                        | Next state       |

|---------------------------------------------|-----|------|------|-----|------------|------------|------------------------------------------------------------------|------------------|

| Read*6                                      | Н   | ×    | ×    | ×   | ×          | DESL       | NOP                                                              | Active           |

|                                             | L   | Н    | Н    | Н   | ×          | NOP        | NOP                                                              | Active           |

|                                             | L   | Н    | Н    | L   | ×          | BST        | BST                                                              | Active           |

|                                             | L   | Н    | L    | Н   | BA, CA, A8 | READ/READA | Interrupting burst read operation to start new read              | Active           |

|                                             | L   | Н    | L    | L   | BA, CA, A8 | WRIT/WRITA | ILLEGAL*13                                                       | _                |

|                                             | L   | L    | Н    | Н   | BA, RA     | ACT        | ILLEGAL*11                                                       | _                |

|                                             | L   | L    | Н    | L   | BA, A8     | PRE, PALL  | Interrupting burst read operation to start pre-charge            | Precharging      |

|                                             | L   | L    | L    | ×   | ×          |            | ILLEGAL                                                          | _                |

| Read with auto-pre-<br>charge* <sup>7</sup> | Н   | ×    | ×    | ×   | ×          | DESL       | NOP                                                              | Precharging      |

|                                             | L   | Н    | Н    | Н   | ×          | NOP        | NOP                                                              | Precharging      |

|                                             | L   | Н    | Н    | L   | ×          | BST        | ILLEGAL                                                          | _                |

|                                             | L   | Н    | L    | Н   | BA, CA, A8 | READ/READA | ILLEGAL*14                                                       | _                |

|                                             | L   | Н    | L    | L   | BA, CA, A8 | WRIT/WRITA | ILLEGAL*14                                                       | _                |

|                                             | L   | L    | Н    | Н   | BA, RA     | ACT        | ILLEGAL*11, 14                                                   | _                |

|                                             | L   | L    | Н    | L   | BA, A8     | PRE, PALL  | ILLEGAL*11, 14                                                   | _                |

|                                             | L   | L    | L    | ×   | ×          |            | ILLEGAL                                                          | _                |

| Write*8                                     | Н   | ×    | ×    | ×   | ×          | DESL       | NOP                                                              | Write recovering |

|                                             | L   | Н    | Н    | Н   | ×          | NOP        | NOP                                                              | Write recovering |

|                                             | L   | Н    | Н    | L   | ×          | BST        | ILLEGAL                                                          | _                |

|                                             | L   | Н    | L    | Н   | BA, CA, A8 | READ/READA | Interrupting burst write operation to start read operation.      | Read/ReadA       |

|                                             | L   | Н    | L    | L   | BA, CA, A8 | WRIT/WRITA | Interrupting burst write operation to start new write operation. | Write/WriteA     |

|                                             | L   | L    | Н    | Н   | BA, RA     | ACT        | ILLEGAL*11                                                       | _                |

|                                             | L   | L    | Н    | L   | BA, A8     | PRE, PALL  | Interrupting write operation to start precharge.                 | Idle             |

|                                             | L   | L    | L    | ×   | ×          |            | ILLEGAL                                                          | _                |

| Write recovering*9                          | Н   | ×    | ×    | ×   | ×          | DESL       | NOP                                                              | Active           |

|                                             | L   | Н    | Н    | Н   | ×          | NOP        | NOP                                                              | Active           |

|                                             | L   | Н    | Н    | L   | ×          | BST        | ILLEGAL                                                          | _                |

|                                             | L   | Н    | L    | Н   | BA, CA, A8 | READ/READA | Starting read operation.                                         | Read/ReadA       |

|                                             | L   | Н    | L    | L   | BA, CA, A8 | WRIT/WRITA | Starting new write operation.                                    | Write/WriteA     |

|                                             | L   | L    | Н    | Н   | BA, RA     | ACT        | ILLEGAL* <sup>11</sup>                                           | _                |

|                                             | L   | L    | Н    | L   | BA, A8     | PRE/PALL   | ILLEGAL*11                                                       | _                |

|                                             | L   | L    | L    | ×   | ×          |            | ILLEGAL                                                          |                  |

| Current state                                 | /CS | /RAS | /CAS | /WE | Address    | Command     | Operation                  | Next state  |

|-----------------------------------------------|-----|------|------|-----|------------|-------------|----------------------------|-------------|

| Write with auto-<br>pre-charge* <sup>10</sup> | Н   | ×    | ×    | ×   | ×          | DESL        | NOP                        | Precharging |

|                                               | L   | Н    | Н    | Н   | ×          | NOP         | NOP                        | Precharging |

|                                               | L   | Н    | Н    | L   | ×          | BST         | ILLEGAL                    | _           |

|                                               | L   | Н    | L    | Н   | BA, CA, A8 | READ/READA  | ILLEGAL* <sup>14</sup>     | _           |

|                                               | L   | Н    | L    | L   | BA, CA, A8 | WRIT/WRIT A | ILLEGAL*14                 | _           |

|                                               | L   | L    | Н    | Н   | BA, RA     | ACT         | ILLEGAL* <sup>11, 14</sup> | _           |

|                                               | L   | L    | Н    | L   | BA, A8     | PRE, PALL   | ILLEGAL* <sup>11, 14</sup> | _           |

|                                               | L   | L    | L    | ×   | ×          |             | ILLEGAL                    | _           |

Remark: H: VIH. L: VIL. x: VIH or VIL

Notes: 1. The DDR SDRAM is in "Precharging" state for tRP after precharge command is issued.

- 2. The DDR SDRAM reaches "IDLE" state tRP after precharge command is issued.

- 3. The DDR SDRAM is in "Refresh" state for tRFC after auto-refresh command is issued.

- 4. The DDR SDRAM is in "Activating" state for tRCDRD or tRCDWR after ACT command is issued.

- 5. The DDR SDRAM is in "Active" state after "Activating" is completed.

- 6. The DDR SDRAM is in "READ" state until burst data have been output and DQ output circuits are turned off.

- 7. The DDR SDRAM is in "READ with auto-precharge" from READA command until burst data has been output and DQ output circuits are turned off.

- 8. The DDR SDRAM is in "WRITE" state from WRIT command to the last burst data are input.

- 9. The DDR SDRAM is in "Write recovering" for tWR after the last data are input.

- 10. The DDR SDRAM is in "Write with auto-precharge" until tWR after the last data has been input.

- 11. This command may be issued for other banks, depending on the state of the banks.

- 12. All banks must be in "IDLE".

- 13. Before executing a write command to stop the preceding burst read operation, BST command must be issued

- 14. The DDR SDRAM supports the concurrent auto-precharge feature, a read with auto-precharge enabled, or a write with auto-precharge enabled, may be followed by any column command to other banks, as long as that command does not interrupt the read or write data transfer, and all other related limitations apply. (E.g. Conflict between READ data and WRITE data must be avoided.)

The minimum delay from a read or write command with auto precharge enabled, to a command to a different bank, is summarized below.

| From command | To command (different bank, non-<br>interrupting command) | Minimum delay (Concurrent AP supported) | Units |

|--------------|-----------------------------------------------------------|-----------------------------------------|-------|

| Read w/AP    | Read or Read w/AP                                         | BL/2                                    | tCK   |

|              | Write or Write w/AP                                       | CL(rounded up)+ (BL/2)                  | tCK   |

|              | Precharge or Activate                                     | 1                                       | tCK   |

| Write w/AP   | Read or Read w/AP                                         | 1 + (BL/2) + tWTR                       | tCK   |

|              | Write or Write w/AP                                       | BL/2                                    | tCK   |

|              | Precharge or Activate                                     | 1                                       | tCK   |

### **Command Truth Table for CKE**

| Current State         | CKE   |   |     |      |      |     |         |                                             |       |

|-----------------------|-------|---|-----|------|------|-----|---------|---------------------------------------------|-------|

|                       | n – 1 | n | /CS | /RAS | /CAS | /WE | Address | Operation                                   | Notes |

| Self refresh          | Н     | × | ×   | ×    | ×    | ×   | ×       | INVALID, CK (n-1) would exit self refresh   |       |

|                       | L     | Н | Н   | ×    | ×    | ×   | ×       | Self refresh recovery                       |       |

|                       | L     | Н | L   | Н    | Н    | ×   | ×       | Self refresh recovery                       |       |

|                       | L     | Н | L   | Н    | L    | ×   | ×       | ILLEGAL                                     |       |

|                       | L     | Н | L   | L    | ×    | ×   | ×       | ILLEGAL                                     |       |

|                       | L     | L | ×   | ×    | ×    | ×   | ×       | Maintain self refresh                       |       |

| Self refresh recovery | Н     | Н | Н   | ×    | ×    | ×   | ×       | Idle after tRC                              |       |

|                       | Н     | Н | L   | Н    | Н    | ×   | ×       | Idle after tRC                              |       |

|                       | Н     | Н | L   | Н    | L    | ×   | ×       | ILLEGAL                                     |       |

|                       | Н     | Н | L   | L    | ×    | ×   | ×       | ILLEGAL                                     |       |

|                       | Н     | L | Н   | ×    | ×    | ×   | ×       | ILLEGAL                                     |       |

|                       | Н     | L | L   | Н    | Н    | ×   | ×       | ILLEGAL                                     |       |

|                       | Н     | L | L   | Н    | L    | ×   | ×       | ILLEGAL                                     |       |

|                       | Н     | L | L   | L    | ×    | ×   | ×       | ILLEGAL                                     |       |

| -                     | Н     | × | ×   | ×    | ×    | ×   |         | INVALID, CK (n – 1) would exit power down   |       |

|                       | L     | Н | Н   | ×    | ×    | ×   | ×       | EXIT power down $\rightarrow$ Idle          |       |

|                       | L     | Н | L   | Н    | Н    | Н   | ×       |                                             |       |

|                       | L     | L | ×   | ×    | ×    | ×   | ×       | Maintain power down mode                    |       |

| All banks idle        | Н     | Н | Н   | ×    | ×    | ×   |         | Refer to operations in Function Truth Table |       |

|                       | Н     | Н | L   | Н    | ×    | ×   |         | Refer to operations in Function Truth Table |       |

|                       | Н     | Н | L   | L    | Н    | ×   |         | Refer to operations in Function Truth Table |       |

|                       | Н     | Н | L   | L    | L    | Н   | ×       | CBR (auto) refresh                          |       |

|                       | Н     | Н | L   | L    | L    | L   | OPCODE  | Refer to operations in Function Truth Table |       |

|                       | Н     | L | Н   | ×    | ×    | ×   |         | Refer to operations in Function Truth Table |       |

|                       | Н     | L | L   | Н    | ×    | ×   |         | Refer to operations in Function Truth Table |       |

|                       | Н     | L | L   | L    | Н    | X   |         | Refer to operations in Function Truth Table |       |

|                       | Н     | L | L   | L    | L    | Н   | ×       | Self refresh                                | 1     |

|                       | Н     | L | L   | L    | L    | L   | OPCODE  | Refer to operations in Function Truth Table |       |

|                       | L     | × | ×   | ×    | ×    | ×   | ×       | Power down                                  | 1     |

| Row active            | Н     | × | ×   | ×    | ×    | ×   | ×       | Refer to operations in Function Truth Table |       |

|                       | L     | × | ×   | ×    | ×    | ×   | ×       | Power down                                  | 1     |

Remark: H: VIH. L: VIL. x: VIH or VIL

Note: Self refresh can be entered only from the all banks idle state. Power down can be entered only from all banks idle or row active state.

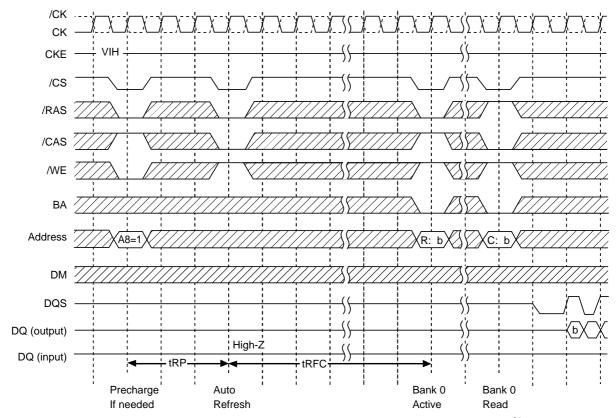

#### Auto-refresh command [REF]

This command executes auto-refresh. The banks and the ROW addresses to be refreshed are internally determined by the internal refresh controller. The average refresh cycle is 7.8 µs. The output buffer becomes High-Z after auto-refresh start. Precharge has been completed automatically after the auto-refresh. The ACT or MRS command can be issued tRFC after the last auto-refresh command.

#### Self-refresh entry [SELF]

This command starts self-refresh. The self-refresh operation continues as long as CKE is held Low. During the self-refresh operation, all ROW addresses are repeated refreshing by the internal refresh controller. A self-refresh is terminated by a self-refresh exit command.

#### Power down mode entry [PDEN]

tPDEN (= 1 cycle) after the cycle when [PDEN] is issued. The DDR SDRAM enters into power-down mode. In power down mode, power consumption is suppressed by deactivating the input initial circuit. Power down mode continues while CKE is held Low. No internal refresh operation occurs during the power down mode. [PDEN] do not disable DLL.

#### Self-refresh exit [SELFX]

This command is executed to exit from self-refresh mode. To issue non-read commands, tSNR has to be satisfied. ((tSNR =)10 cycles for tCK = 7.5 ns or 12 cycles for tCK = 6.0 ns after [SELFX]) To issue read command, tSRD has to be satisfied to adjust DOUT timing by DLL. (200 cycles after [SELFX]) After the exit, input auto-refresh command within 7.8  $\mu$ s.

### Power down exit [PDEX]

The DDR SDRAM can exit from power down mode tPDEX (1 cycle min.) after the cycle when [PDEX] is issued.

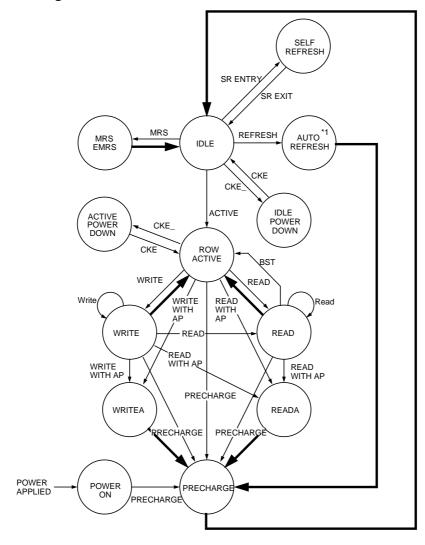

# **Simplified State Diagram**

Automatic transition after completion of command.Transition resulting from command input.

Note: 1. After the auto-refresh operation, precharge operation is performed automatically and enter the IDLE state.

#### Operation of the DDR SDRAM

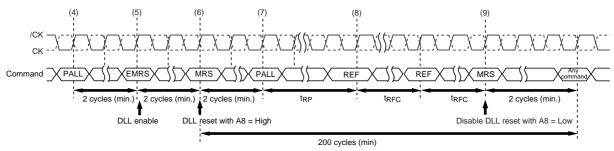

#### **Power-up Sequence**

- (1) Apply power and maintain CKE at an LVCMOS low state (all other inputs are undefined). Apply VDD before or at the same time as VDDQ.

- Apply VDDQ before or at the same time as VTT and VREF.

- (2) Start clock and maintain stable condition for a minimum of 200µs.

- (3) After the minimum 200µs of stable power and clock (CK, /CK), apply NOP and take CKE high.

- (4) Issue precharge all command for the device.

- (5) Issue EMRS to enable DLL.

- (6) Issue a mode register set command (MRS) for "DLL reset" with bit A8 set to high (An additional 200 cycles of clock input is required to lock the DLL after every DLL reset).

- (7) Issue precharge all command for the device.

- (8) Issue 2 or more auto-refresh commands.

- (9) Issue a mode register set command to initialize device operation with bit A8 set to low in order to avoid resetting the DLL.

Power-up Sequence after CKE Goes High

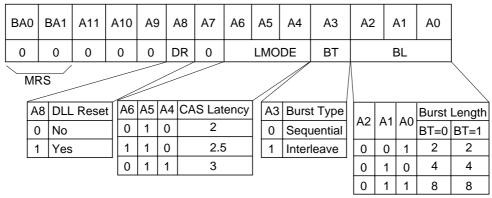

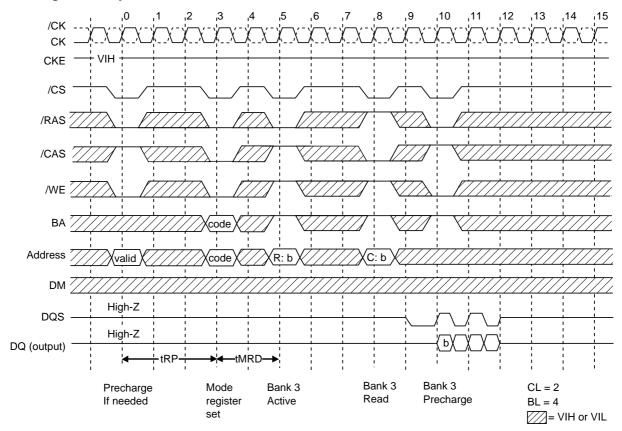

#### Mode Register and Extended Mode Register Set

There are two mode registers, the mode register and the extended mode register so as to define the operating mode. Parameters are set to both through the A0 to the A11 and BA0, BA1 pins by the mode register set command [MRS] or the extended mode register set command [EMRS]. The mode register and the extended mode register are set by inputting signal via the A0 to the A11 and BA0, BA1 during mode register set cycles. BA0 and BA1 determine which one of the mode register or the extended mode register are set. Prior to a read or a write operation, the mode register must be set.

Remind that no other parameters shown in the table bellow are allowed to input to the registers.

Mode Register Set [MRS] (BA0 = 0, BA1 = 0)

**ELPIDA**

Extended Mode Register Set [EMRS] (BA0 = 1, BA1 = 0)

# **Burst Operation**

The burst type (BT) and the first three bits of the column address determine the order of a data out.

Burst length = 2

| Starting Ad. | Addressing | (decimal)  |

|--------------|------------|------------|

| A0           | Sequence   | Interleave |

| 0            | 0, 1,      | 0, 1,      |

| 1            | 1, 0,      | 1, 0,      |

Burst length = 4

| Starting Ad. |    | Addressing(decimal)     |

|--------------|----|-------------------------|

| A1           | A0 | Sequence Interleave     |

| 0            | 0  | 0, 1, 2, 3, 0, 1, 2, 3, |

| 0            | 1  | 1, 2, 3, 0, 1, 0, 3, 2, |

| 1            | 0  | 2, 3, 0, 1, 2, 3, 0, 1, |

| 1            | 1  | 3, 0, 1, 2, 3, 2, 1, 0, |

# Burst length = 8

|              | But to figure 5 |    |                         |                         |  |  |  |

|--------------|-----------------|----|-------------------------|-------------------------|--|--|--|

| Starting Ad. |                 |    | Addressing(decimal)     |                         |  |  |  |

| A            | 2 A1            | A0 | Sequence                | Interleave              |  |  |  |

|              | 0 0             | 0  | 0, 1, 2, 3, 4, 5, 6, 7, | 0, 1, 2, 3, 4, 5, 6, 7, |  |  |  |

|              | 0 0             | 1  | 1, 2, 3, 4, 5, 6, 7, 0, | 1, 0, 3, 2, 5, 4, 7, 6, |  |  |  |

| (            | 0 1             | 0  | 2, 3, 4, 5, 6, 7, 0, 1, | 2, 3, 0, 1, 6, 7, 4, 5, |  |  |  |

|              | 0 1             | 1  | 3, 4, 5, 6, 7, 0, 1, 2, | 3, 2, 1, 0, 7, 6, 5, 4, |  |  |  |

|              | 1 0             | 0  | 4, 5, 6, 7, 0, 1, 2, 3, | 4, 5, 6, 7, 0, 1, 2, 3, |  |  |  |

|              | 1 0             | 1  | 5, 6, 7, 0, 1, 2, 3, 4, | 5, 4, 7, 6, 1, 0, 3, 2, |  |  |  |

|              | 1 1             | 0  | 6, 7, 0, 1, 2, 3, 4, 5, | 6, 7, 4, 5, 2, 3, 0, 1, |  |  |  |

|              | 1 1             | 1  | 7, 0, 1, 2, 3, 4, 5, 6, | 7, 6, 5, 4, 3, 2, 1, 0, |  |  |  |

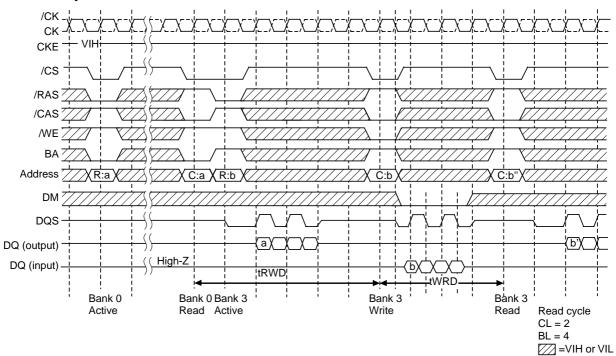

#### **Read/Write Operations**

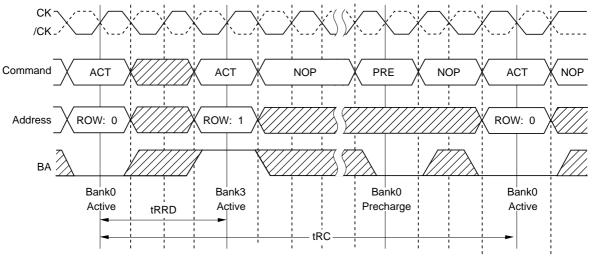

#### Bank active

A read or a write operation begins with the bank active command [ACT]. The bank active command determines a bank address and a row address. For the bank and the row, a read or a write command can be issued tRCDRD or tRCDWR after the ACT is issued.

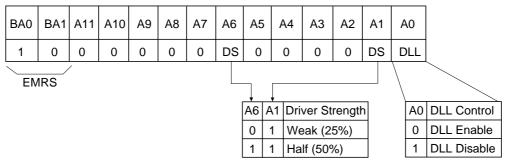

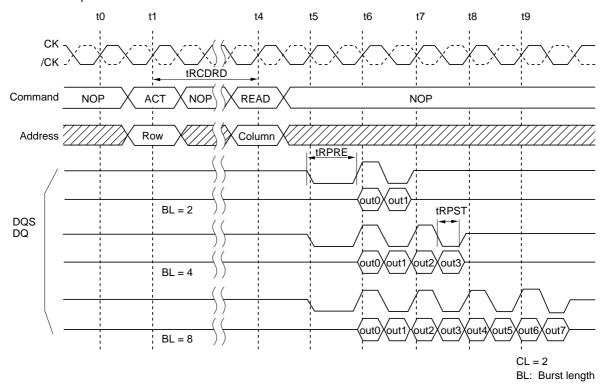

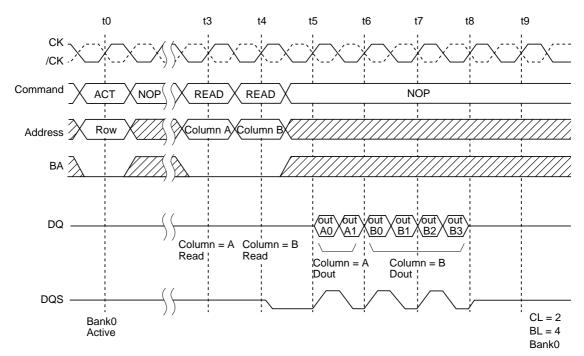

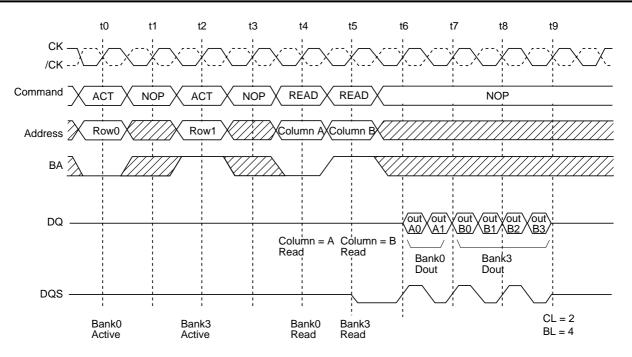

#### Read operation

The burst length (BL), the /CAS latency (CL) and the burst type (BT) of the mode register are referred when a read command is issued. The burst length (BL) determines the length of a sequential output data by the read command that can be set to 2, 4, or 8. The starting address of the burst read is defined by the column address, the bank select address which are loaded via the A0 to A11 and BA0, BA1 pins in the cycle when the read command is issued. The data output timing are characterized by CL and tAC. The read burst start CL • tCK + tAC (ns) after the clock rising edge where the read command are latched. The DDR SDRAM output the data strobe through DQS simultaneously with data. tRPRE prior to the first rising edge of the data strobe, the DQS are driven Low from VTT level. This low period of DQS is referred as read preamble. The burst data are output coincidentally at both the rising and falling edge of the data strobe. The DQ pins become High-Z in the next cycle after the burst read operation completed. tRPST from the last falling edge of the data strobe, the DQS pins become High-Z. This low period of DQS is referred as read postamble.

**Read Operation (Burst Length)**

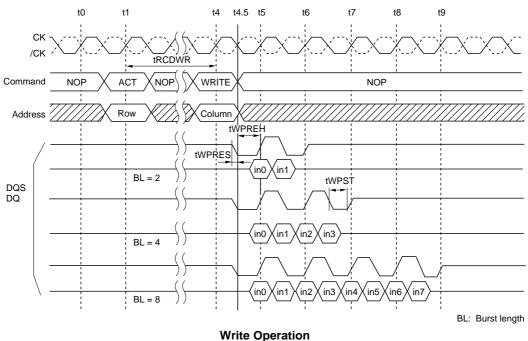

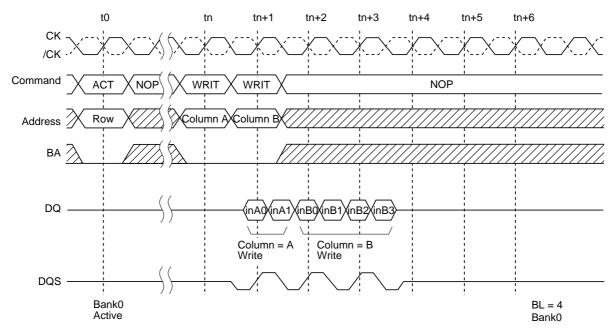

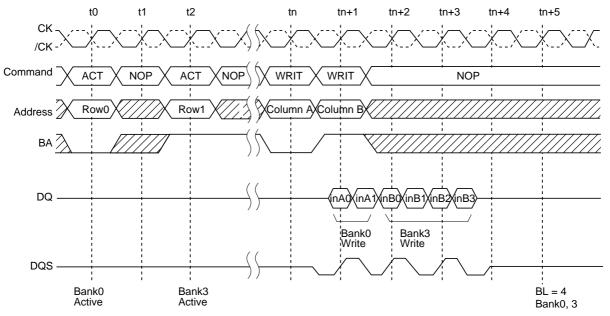

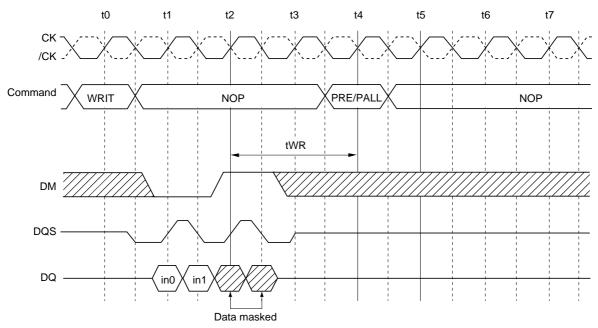

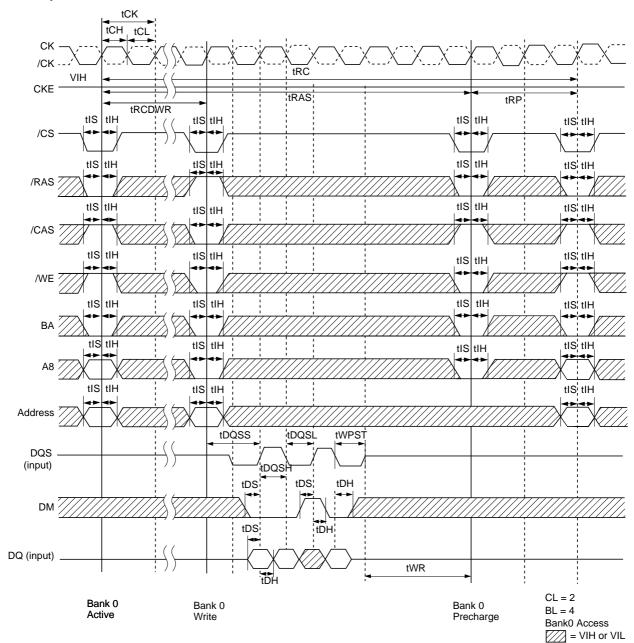

### Write operation

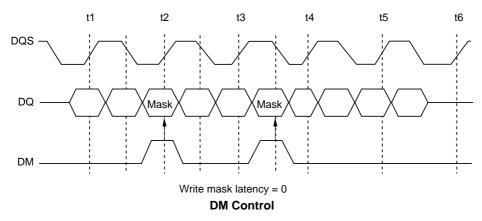

The burst length (BL) and the burst type (BT) of the mode register are referred when a write command is issued. The burst length (BL) determines the length of a sequential data input by the write command that can be set to 2, 4, or 8. The latency from write command to data input is fixed to 1. The starting address of the burst read is defined by the column address, the bank select address which are loaded via the A0 to A11, BA0 to BA1 pins in the cycle when the write command is issued. DQS should be input as the strobe for the input-data and DM as well during burst operation. tWPREH prior to the first rising edge of the DQS should be set to Low and tWPST after the last falling edge of the data strobe can be set to High-Z. The leading low period of DQS is referred as write preamble. The last low period of DQS is referred as write postamble.

#### **Burst Stop**

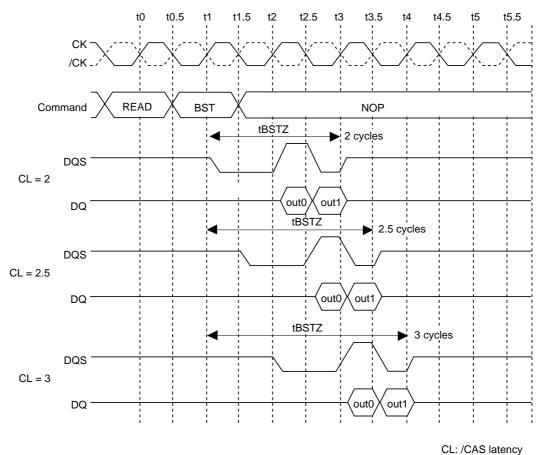

### Burst stop command during burst read

The burst stop (BST) command is used to stop data output during a burst read. The BST command stops the burst read and sets the output buffer to High-Z. tBSTZ (= CL) cycles after a BST command issued, the DQ pins become High-Z. The BST command is not supported for the burst write operation. Note that bank address is not referred when this command is executed.

**Burst Stop during a Read Operation**

#### **Auto Precharge**

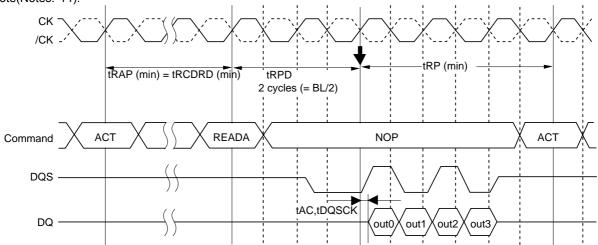

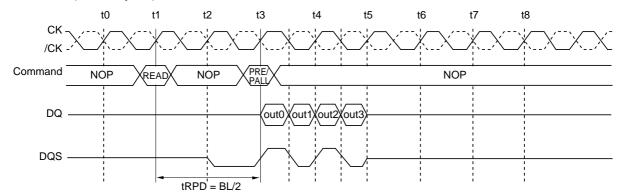

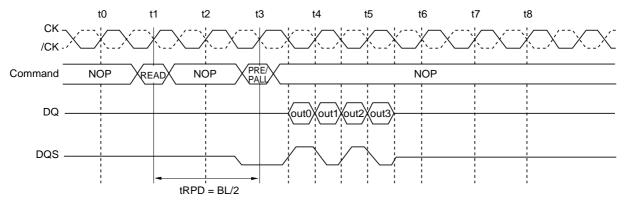

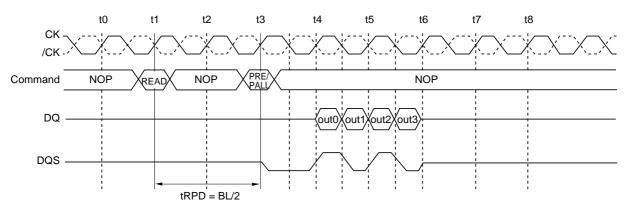

#### Read with auto-precharge

The precharge is automatically performed after completing a read operation. The precharge starts tRPD (BL/2) cycle after READA command input. tRAP specification for READA allows a read command with auto precharge to be issued to a bank that has been activated (opened) but has not yet satisfied the tRAS (min) specification. A column command to the other active bank can be issued the next cycle after the last data output. Read with auto-precharge command does not limit row commands execution for other bank. Refer to 'Function truth table and related note(Notes.\*14).

Note: Internal auto-precharge starts at the timing indicated by "\\ \dlapsis ".

Read with auto-precharge

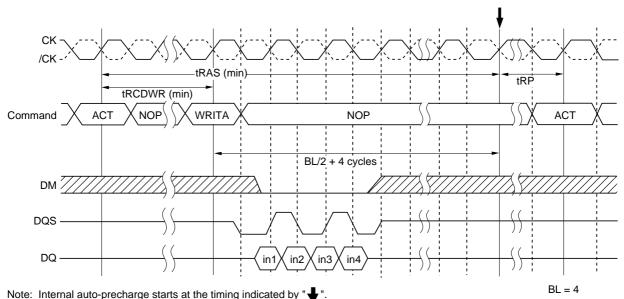

### Write with auto-precharge

The precharge is automatically performed after completing a burst write operation. The precharge operation is started (BL/ 2 + 4) cycles after WRITA command issued. A column command to the other banks can be issued the next cycle after the internal precharge command issued. Write with auto-precharge command does not limit row commands execution for other bank. Refer to the 'Read with Auto-Precharge Enabled, Write with Auto-Precharge Enabled' section. Refer to 'Function truth table and related note (Notes.\*14).

Burst Write (BL = 4)

ELPIDA

#### **Command Intervals**

#### A Read command to the consecutive Read command Interval

Destination row of the consecutive read command

|    | Bank<br>address | Row address | State  | Operation                                                                                                                                                                                                                                                           |

|----|-----------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | Same            | Same        | ACTIVE | The consecutive read can be performed after an interval of no less than 1 cycle to interrupt the preceding read operation.                                                                                                                                          |

| 2. | Same            | Different   | _      | Precharge the bank to interrupt the preceding read operation. tRP after the precharge command, issue the ACT command. tRCDRD after the ACT command, the consecutive read command can be issued. See 'A read command to the consecutive precharge interval' section. |

| 3. | Different       | Any         | ACTIVE | The consecutive read can be performed after an interval of no less than 1 cycle to interrupt the preceding read operation.                                                                                                                                          |

|    |                 |             | IDLE   | Precharge the bank without interrupting the preceding read operation. tRP after the precharge command, issue the ACT command. tRCDRD after the ACT command, the consecutive read command can be issued.                                                             |

READ to READ Command Interval (same ROW address in the same bank)

**READ to READ Command Interval (different bank)**

### A Write command to the consecutive Write command Interval

Destination row of the consecutive write command

|    | communic        |             |        | _                                                                                                                                                                                                                                                                      |  |

|----|-----------------|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    | Bank<br>address | Row address | State  | Operation                                                                                                                                                                                                                                                              |  |

| 1. | Same            | Same        | ACTIVE | The consecutive write can be performed after an interval of no less than 1 cycle to interrupt the preceding write operation.                                                                                                                                           |  |

| 2. | Same            | Different   | _      | Precharge the bank to interrupt the preceding write operation. tRP after the precharge command, issue the ACT command. tRCDWR after the ACT command, the consecutive write command can be issued. See 'A write command to the consecutive precharge interval' section. |  |

| 3. | Different       | Any         | ACTIVE | The consecutive write can be performed after an interval of no less than 1 cycle to interrupt the preceding write operation.                                                                                                                                           |  |

|    |                 |             | IDLE   | Precharge the bank without interrupting the preceding write operation. tRP after the precharge command, issue the ACT command. tRCDWR after the ACT command, the consecutive write command can be issued.                                                              |  |

WRITE to WRITE Command Interval (same ROW address in the same bank)

WRITE to WRITE Command Interval (different bank)

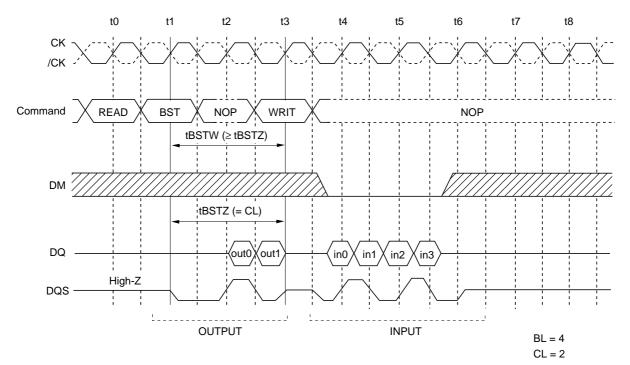

### A Read command to the consecutive Write command interval with the BST command

Destination row of the consecutive write command

|    | oommana         |             |        | <u> </u>                                                                                                                                                                                                                                                             |  |

|----|-----------------|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    | Bank<br>address | Row address | State  | Operation                                                                                                                                                                                                                                                            |  |

| 1. | Same            | Same        | ACTIVE | Issue the BST command. tBSTW (≥ tBSTZ) after the BST command, the consecutive write command can be issued.                                                                                                                                                           |  |

| 2. | Same            | Different   | _      | Precharge the bank to interrupt the preceding read operation. tRP after the precharge command, issue the ACT command. tRCDWR after the ACT command, the consecutive write command can be issued. See 'A read command to the consecutive precharge interval' section. |  |

| 3. | Different       | Any         | ACTIVE | Issue the BST command. tBSTW (≥ tBSTZ) after the BST command, the consecutive write command can be issued.                                                                                                                                                           |  |

|    |                 |             | IDLE   | Precharge the bank independently of the preceding read operation. tRP after the precharge command, issue the ACT command. tRCDWR after the ACT command, the consecutive write command can be issued.                                                                 |  |

**READ to WRITE Command Interval**

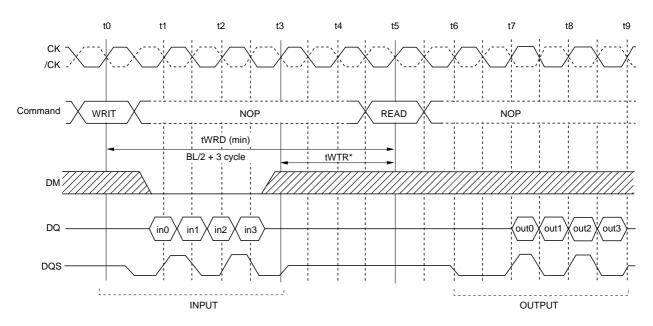

### A Write command to the consecutive Read command interval: To complete the burst operation

Destination row of the consecutive read command

|    |                 |                   |        | <u> </u>                                                                                                                                                                                                                                                         |  |

|----|-----------------|-------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    | Bank<br>address | Row address State |        | Operation                                                                                                                                                                                                                                                        |  |

| 1. | Same            | Same              | ACTIVE | To complete the burst operation, the consecutive read command should be performed tWRD (= BL/ 2 + 3) after the write command.                                                                                                                                    |  |

| 2. | Same            | Different         | _      | Precharge the bank tWPD after the preceding write command. tRP after the precharge command, issue the ACT command. tRCDRD after the ACT command, the consecutive read command can be issued. See 'A read command to the consecutive precharge interval' section. |  |

| 3. | Different       | Any               | ACTIVE | To complete a burst operation, the consecutive read command should be performed tWRD (= BL/ 2 + 3) after the write command.                                                                                                                                      |  |

|    |                 |                   | IDLE   | Precharge the bank independently of the preceding write operation. tRP after the precharge command, issue the ACT command. tRCDRD after the ACT command, the consecutive read command can be issued.                                                             |  |

Note: tWTR is referenced from the first positive CK edge after the last desired data in pair tWTR.

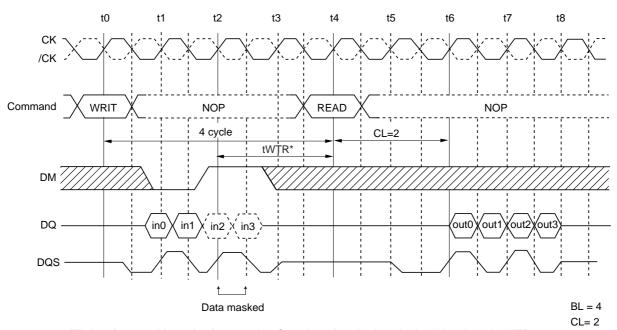

BL = 4

CL = 2

**WRITE to READ Command Interval**

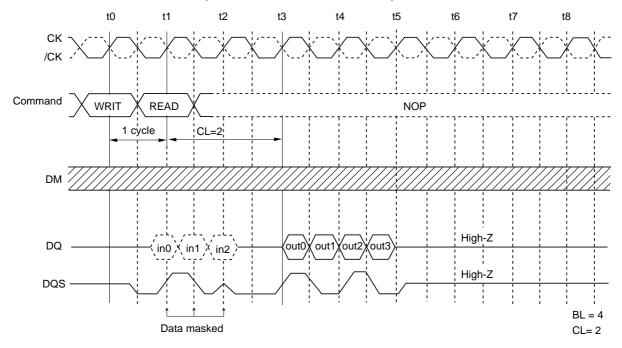

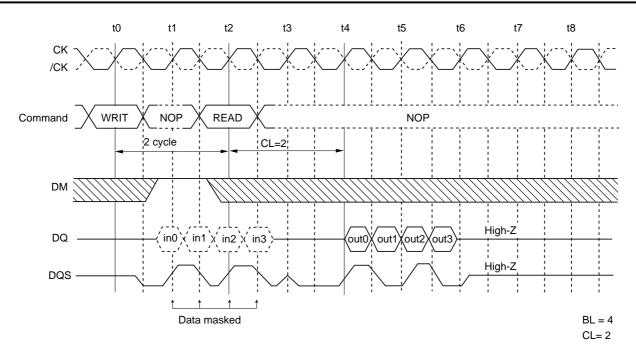

### A Write command to the consecutive Read command interval: To interrupt the write operation

Destination row of the consecutive read command

|    |                 |             |        | _                                                                                                                                                                                                    |  |

|----|-----------------|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    | Bank<br>address | Row address | State  | Operation                                                                                                                                                                                            |  |

| 1. | Same            | Same        | ACTIVE | DM must be input 1 cycle prior to the read command input to prevent from being written invalid data. In case, the read command is input in the next cycle of the write command, DM is not necessary. |  |